- 您现在的位置:买卖IC网 > Sheet目录342 > MCBSTM32EXL (Keil)BOARD EVALUATION FOR STM32F103ZE

�� �

�

�

�Advanced-control� timers� (TIM1&TIM8)�

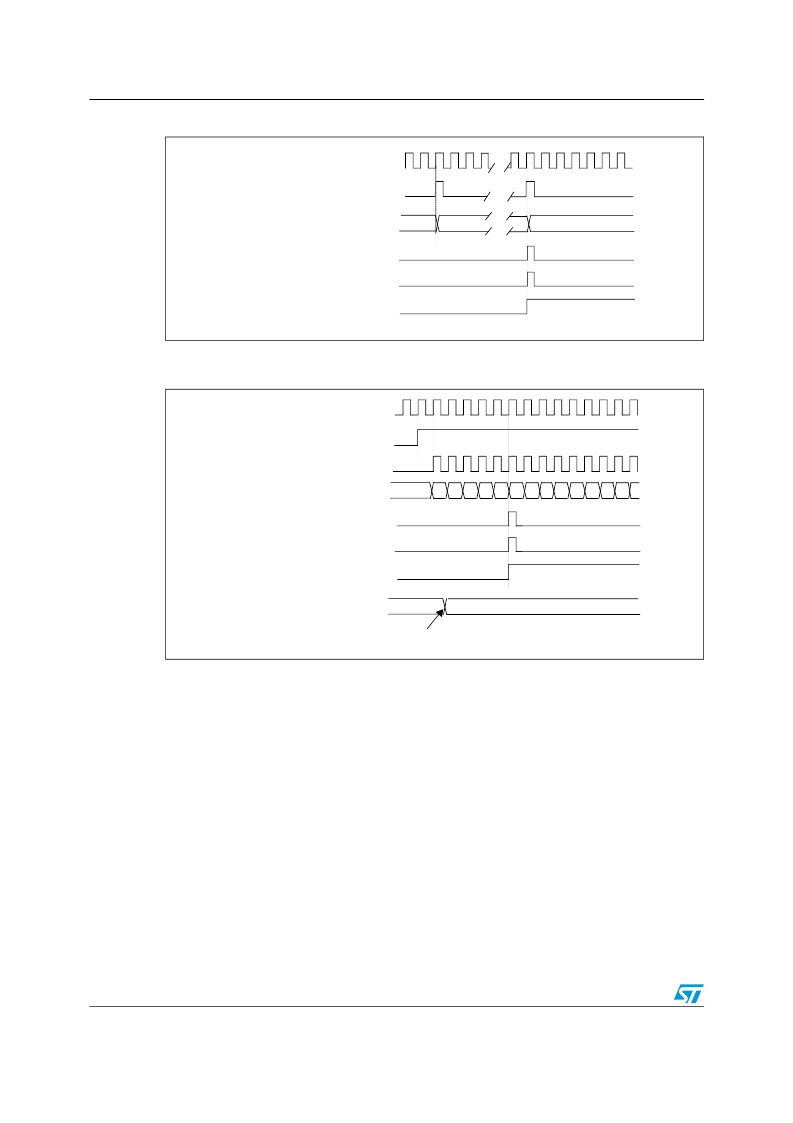

�Figure� 63.� Counter� timing� diagram,� internal� clock� divided� by� N�

�CK_PSC�

�Timer� clock� =� CK_CNT�

�RM0008�

�Counter� register�

�20�

�1F�

�00�

�36�

�Counter� underflow�

�Update� event� (UEV)�

�Update� interrupt� flag� (UIF)�

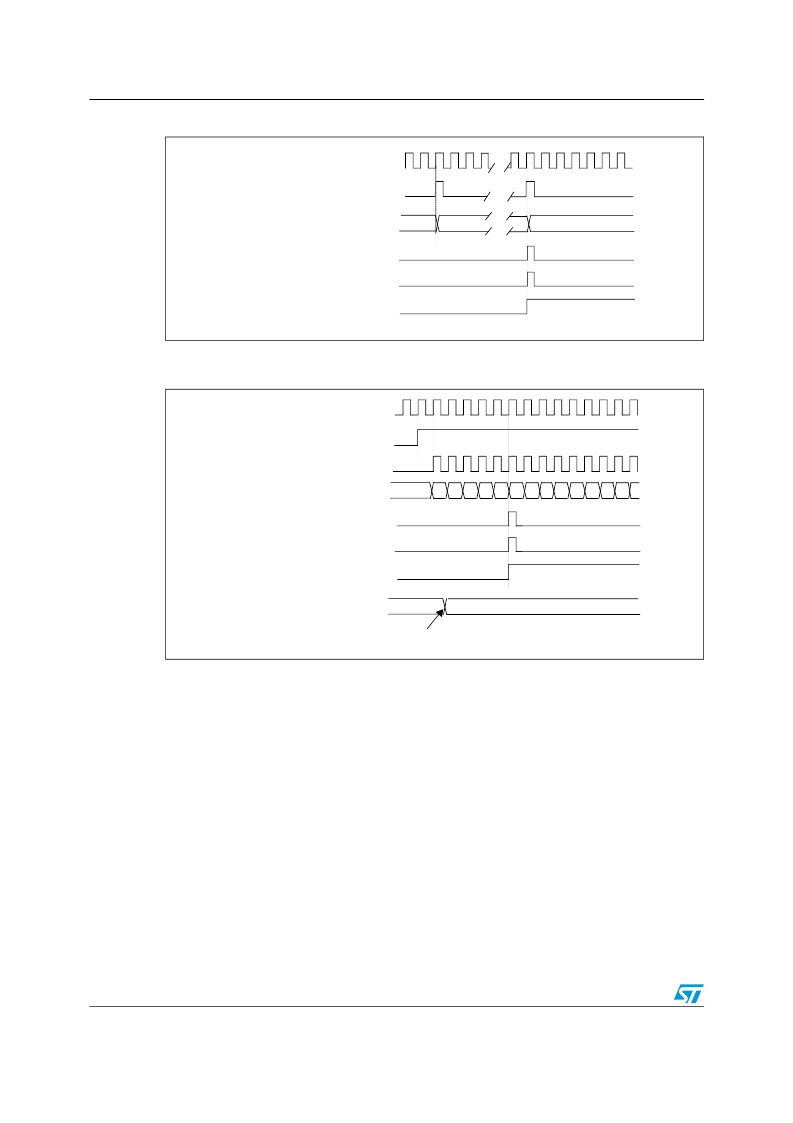

�Figure� 64.� Counter� timing� diagram,� update� event� when� repetition� counter� is� not�

�used�

�CK_PSC�

�CEN�

�Timer� clock� =� CK_CNT�

�Counter� register�

�Counter� underflow�

�Update� event� (UEV)�

�Update� interrupt� flag� (UIF)�

�Auto-reload� register�

�05�

�FF�

�04 03 02 01 00 36 35 34 33 32 31 30 2F�

�36�

�Write� a� new� value� in� TIMx_ARR�

�Center-aligned� mode� (up/down� counting)�

�In� center-aligned� mode,� the� counter� counts� from� 0� to� the� auto-reload� value� (content� of� the�

�TIMx_ARR� register)� –� 1,� generates� a� counter� overflow� event,� then� counts� from� the� auto-�

�reload� value� down� to� 1� and� generates� a� counter� underflow� event.� Then� it� restarts� counting�

�from� 0.�

�In� this� mode,� the� DIR� direction� bit� in� the� TIMx_CR1� register� cannot� be� written.� It� is� updated�

�by� hardware� and� gives� the� current� direction� of� the� counter.�

�The� update� event� can� be� generated� at� each� counter� overflow� and� at� each� counter� underflow�

�or� by� setting� the� UG� bit� in� the� TIMx_EGR� register� (by� software� or� by� using� the� slave� mode�

�controller)� also� generates� an� update� event.� In� this� case,� the� counter� restarts� counting� from�

�0,� as� well� as� the� counter� of� the� prescaler.�

�The� UEV� update� event� can� be� disabled� by� software� by� setting� the� UDIS� bit� in� the� TIMx_CR1�

�register.� This� is� to� avoid� updating� the� shadow� registers� while� writing� new� values� in� the�

�preload� registers.� Then� no� update� event� occurs� until� UDIS� bit� has� been� written� to� 0.�

�However,� the� counter� continues� counting� up� and� down,� based� on� the� current� auto-reload�

�value.�

�262/995�

�Doc� ID� 13902� Rev� 9�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

MCBTMPM330

BOARD EVAL TOSHIBA TMPM330 SER

MCIMX25WPDKJ

KIT DEVELOPMENT WINCE IMX25

MCIMX53-START-R

KIT DEVELOPMENT I.MX53

MCM69C432TQ20

IC CAM 1MB 50MHZ 100LQFP

MCP1401T-E/OT

IC MOSFET DRVR INV 500MA SOT23-5

MCP1403T-E/MF

IC MOSFET DRIVER 4.5A DUAL 8DFN

MCP1406-E/SN

IC MOSFET DVR 6A 8SOIC

MCP14628T-E/MF

IC MOSFET DVR 2A SYNC BUCK 8-DFN

相关代理商/技术参数

MCBSTM32EXLU

功能描述:开发板和工具包 - ARM EVAL BOARD + ULINK2 FOR STM32F103ZG

RoHS:否 制造商:Arduino 产品:Development Boards 工具用于评估:ATSAM3X8EA-AU 核心:ARM Cortex M3 接口类型:DAC, ICSP, JTAG, UART, USB 工作电源电压:3.3 V

MCBSTM32EXLU-ED

制造商:ARM Ltd 功能描述:KEIL STM STM32EXL EVAL BOARD

MCBSTM32EXLUME

功能描述:开发板和工具包 - ARM EVAL BOARD + ULINKME FOR STM32F103ZG

RoHS:否 制造商:Arduino 产品:Development Boards 工具用于评估:ATSAM3X8EA-AU 核心:ARM Cortex M3 接口类型:DAC, ICSP, JTAG, UART, USB 工作电源电压:3.3 V

MCBSTM32F200

功能描述:开发板和工具包 - ARM EVAL BOARD FOR STM STM32F207IG

RoHS:否 制造商:Arduino 产品:Development Boards 工具用于评估:ATSAM3X8EA-AU 核心:ARM Cortex M3 接口类型:DAC, ICSP, JTAG, UART, USB 工作电源电压:3.3 V

MCBSTM32F200U

功能描述:开发板和工具包 - ARM EVAL BOARD FOR STM STM32F207IG + ULINK2

RoHS:否 制造商:Arduino 产品:Development Boards 工具用于评估:ATSAM3X8EA-AU 核心:ARM Cortex M3 接口类型:DAC, ICSP, JTAG, UART, USB 工作电源电压:3.3 V

MCBSTM32F200UME

功能描述:开发板和工具包 - ARM EVAL BOARD FOR STM STM32F207IG ULINK-ME

RoHS:否 制造商:Arduino 产品:Development Boards 工具用于评估:ATSAM3X8EA-AU 核心:ARM Cortex M3 接口类型:DAC, ICSP, JTAG, UART, USB 工作电源电压:3.3 V

MCBSTM32F200UME-ED

制造商:ARM Ltd 功能描述:KEIL STM32F207IG EVAL BOARD

MCBSTM32F400

功能描述:开发板和工具包 - ARM EVAL BOARD FOR STM STM32F407IG

RoHS:否 制造商:Arduino 产品:Development Boards 工具用于评估:ATSAM3X8EA-AU 核心:ARM Cortex M3 接口类型:DAC, ICSP, JTAG, UART, USB 工作电源电压:3.3 V